# TLM-based numerical extraction for CMOS-compatible N<sup>+</sup>-InGaAs ohmic contacts on 200mm Si substrates

<u>A. Lombrez</u><sup>1,2\*</sup>, A. Divay<sup>2</sup>, H. Boutry<sup>2</sup>, L. Colas<sup>2</sup>, N. Coudurier<sup>2</sup>, S. Altazin<sup>2</sup>, T. Baron<sup>1</sup> <sup>1</sup>Univ. Grenoble Alpes, CNRS, CEA/LETI-Minatec, Grenoble INP, LTM, Grenoble 38054 France

<sup>2</sup> Univ. Grenoble Alpes, CEA, LETI, 38054 Grenoble, France

### **Results and discussion**

Abstract – We report the results of a TLM-based numerical extraction methodology applied on CMOS-compatible n<sup>+</sup>-InGaAs ohmic contacts integrated with dielectrics on 200mm Si substrate. We obtained state-of-the-art level  $\rho_c = 7,5.10^{-8}$  ohm.cm<sup>2</sup> for relevant contact dimensions (THz HBT for 6G). This methodology is first described and calibrated using contacts on SOI.

#### Introduction

As the demand for increased data rates is growing in telecommunications, 6G/sub-millimeter Wave (submmW) aims to achieve the desired capacity through operation at very high frequencies (~300GHz). InPbased devices are nowadays the best-in-class devices to operate efficiently at these frequencies [1]. Achieving high performance and stable ohmic contacts using CMOS-compatible metallization is a first challenge to overcome to address HBT-InP based circuits integration on large scale silicon. To obtain 6G/sub-mmW requirements such as THz Maximum Frequency of Oscillation, values in the order of 10<sup>-8</sup> ohm.cm<sup>2</sup> for the specific contact resistivity are required mainly for emitter and base contacts of the transistor [2], as HBT frequency performance is directly linked to the ohmic contacts quality. Structures with dimensions as close as possible to the common THz HBTs emitter, base and collector contact dimensions are thus necessary for accurate contact evaluation.

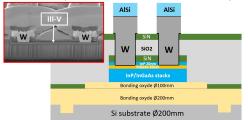

## Device description and TLM interpretation

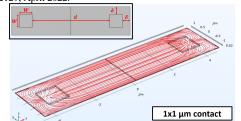

TLM structures with contact dimensions from 5x5µm to  $0.35 \times 0.35 \mu m$  are formed on integrated In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP stacks on a 200mm silicon manufacturing platform (Fig. 1). Structures were first measured following the classical TLM extraction methodology. However, interpreting the resistivity results is not straightforward as the mesa geometry of our structures is incompatible with usual TLM assumptions [3]. Indeed, as the  $\delta$  distance (invariant versus contact geometry) becomes significant for low contact dimensions, the global current path within the structure geometry has to be considered, see Fig. 2. To address this issue, we directly considered our contact and mesa geometries using numerical simulation (COMSOL software). Borders of the structures are considered fully isolated and resistivity induced by the contact metal stack is ignored, as it has been evaluated to be negligible. Contact resistivity and conductivity values are respectively set to the metal/semiconductor interfaces and to the semiconductor layer.

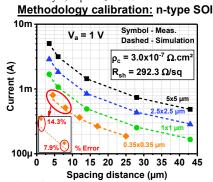

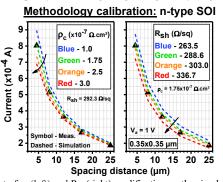

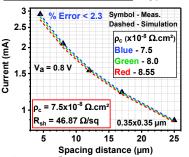

To calibrate our extraction methodology, we first used our numerical model on n-type SOI stacks (Fig. 3). Initial  $\rho_c$  and  $R_{sh}$  values for simulation were taken from TLM measurements realized on the largest available contact area (5x5µm). As Fig. 3 shows, we can correctly assess the measured current levels for larger contact dimensions with the initial  $\rho_c$  and  $R_{sh}$  values. However, for smaller ones (0.35x0.35µm), significant errors appear for low spacing distance (d) values, meaning that these contacts are not accurately modeled. We thus adjust the  $\rho_c$  and  $R_{sh}$  values by determining how they individually affect the fitting of the curves for the 0.35x0.35µm geometry, see Fig. 4. Values providing the best overall fit along all spacing distances (d) are retained and reinjected into the simulation. We found out this allows to assess a single value of  $\rho_{c}$  and  $R_{sh}$  for all contact geometries, as less than 3.5% error is obtained between measured and simulated current levels. Our numerical solution thus properly models the contact for all dimensions. Numerically extracted R<sub>sh</sub> and  $\rho_c$  are then compared with classical TLM extraction. Sheet resistivity is only modified by +4% whereas  $\rho_c$  can be over-evaluated by ~50% using classical TLM extraction methodology, depending on the contact geometry (Table 1). This confirms that classical TLM interpretation is limited for scaled contact geometries as in our case. This methodology has then be used to extract the contact resistivity of CMOS-compatible Tibased contact on n<sup>+</sup>-InGaAs layers. Extraction for  $0.35 \times 0.35 \mu m$  contact leads to  $\rho_c = 7, 5.10^{-8}$  ohm.cm<sup>2</sup> value (Fig. 5). It is 15.3% less than the value extracted using classical TLM interpretation. Such  $\rho_c$  value on n<sup>+</sup>-InGaAs is comparable to the state-of-the-art, see Table 2. This is a convincing and encouraging result for future HBT-InP emitter and collector contacts fully integrated in silicon environment, with values of 10<sup>-8</sup> ohm.cm<sup>2</sup>.

**Conclusion** – A TLM-based numerical extraction has been proposed to properly extract the sheet resistance and contact resistivity of CMOS-compatible ohmic contacts on n-InGaAs layers. This refinement allows to reduce errors by 15.3% compared to classical TLM extraction for such scaled contacts. The obtained  $\rho_c$  value is compatible with 6G THz applications and comparable to the state-of-the-art.

*Acknowledgements* – This work was supported by the French Public Authorities ANR via Carnot Institute Funding, the Electronic Research Program (PEPR T-REX 6G) and the French Renatech network.

<sup>\*</sup> Corresponding author: email: antoine.lombrez@cea.fr

*References:* [1] H. Wang et al., [Online], Available: <u>https://ideas.ethz.ch/Surveys/pa-survey.html</u> [2] M. Rodwell et al., 2008 IEEE Compound Semiconductor Integrated Circuits Symposium, Monterey, CA, USA, 2008, pp. 1-3 [3] L. Basset et al., Solar Energy Materials and Solar Cells 230 (2021): 111255 [4] N. Waldron et al., ECS Transactions 45.4 (2012): 115. [5] V. Djara et al., 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 2015, pp. T176-T177 [6] J. Lin et al., IEEE Transactions on Electron Devices, vol. 63, no. 3, pp. 1020-1026, March 2016 [7] R. T. P. Lee et al., 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 2014, pp. 32.4.1-32.4.4 [8] R. Dormaier et al., Journal of Vacuum Science & Technology B 30.3 (2012). [9] A. M. Arabhavi et al., IEEE Transactions on Electron Devices, vol. 69, no. 4, pp. 2122-2129, April 2022.

Fig. 1: Schematic view and FIB-STEM picture of the technology stack embedded in dielectrics. The Ti/TiN/W/Ti/AlSi metallization is deposited to contact the n+-InGaAs layer, doped  $N_d = 5.10^{19}$  cm<sup>-3</sup>.

Fig. 3: Comparison of measured and simulated electric currents according to geometries. Smaller contacts (relevant for our application) are not accurately modeled using  $\rho_c$  and  $R_{sh}$  from 5x5µm contacts obtained from classical TLM analysis.

#### Methodology calibration: n-type SOI

| Contact geometry<br>(µm) | Classical TLM<br>$\rho_c$ extraction<br>$(10^{-7} \text{ ohm.cm}^2)$ | Simulation $\rho_c$<br>extraction<br>$(10^{-7} \text{ ohm.cm}^2)$ | % Error  |

|--------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------|----------|

| 5 x 5                    | 3.04                                                                 |                                                                   | - 42.4 % |

| 2.5 x 2.5                | 3.60                                                                 | 1.75                                                              | -51.4 %  |

| 1 x 1                    | 2.15                                                                 | 1.75                                                              | - 18.4 % |

| 0.35 x 0.35              | 1.84                                                                 |                                                                   | - 4.9 %  |

$\begin{array}{l} \textbf{Table 1:} \ \rho_c \ \text{extraction difference between classical TLM methodology and} \\ \text{simulation based on n-doped SOI stacks. Large contact extraction leads to} \\ \sim 50\% \ \text{error. Our simulation allows to fit all results with only one } \rho_c \ \text{value.} \end{array}$

Fig. 2: Reproduction of measured ohmic contact-based structures for TLM extraction of electrical parameters with a COMSOL assisted methodology. 3D current flow is adequately assessed regarding mesa geometry (large  $\delta$  distance).

Fig. 4: Impact of  $\rho_c$  (left) and  $R_{sh}$  (right) modification on the simulated electric current curves.  $\rho_c$  affects the offset and the slope of the curves for small *d* values (left). Modifying  $R_{sh}$  (right) applies a global offset to the curves.

Methodology application: n-type InGaAs

Fig. 5:  $\rho_c$  extraction (7,5.10<sup>-8</sup> ohm.cm<sup>2</sup>) from ohmic contacts on n-type InGaAs in CMOS-compatible integration using our methodology. Standard TLM extraction yields 8,85.10<sup>-8</sup> ohm.cm<sup>2</sup> (15.3% error).

| function and we to fit an results with only one pt value.     |                |             | . extraction fields 0,05.10 |                         | omm.em (13.570 error).  |                          |             |

|---------------------------------------------------------------|----------------|-------------|-----------------------------|-------------------------|-------------------------|--------------------------|-------------|

|                                                               | This work      | [4]         | [5]                         | [6]                     | [7]                     | [8]                      |             |

| n-InGaAs doping level<br>(10 <sup>19</sup> cm <sup>-3</sup> ) | 5.0            | ~7.5        | Not specified               | 3.0                     | 1.0                     | 1.0                      |             |

| Contact metal                                                 | Ti (/TiN/W)    | Ti (/TiN/W) | W                           | Mo (/W)                 | Mo (/Ti/TiN/W)          | Ti (/Pt/Au)              | used in [9] |

| CMOS-compatible<br>process integration                        | Yes            | Yes         | Yes                         | No                      | No                      | No                       |             |

| Substrate                                                     | Si 200mm       | Si 200mm    | Si 200mm                    | Si<br>(Ø not specified) | Si<br>(Ø not specified) | InP<br>(Ø not specified) |             |

| Contact area for<br>resistivity extraction                    | 0.35 x 0.35 μm | 0.05 x 2 μm | 0.09 x 0.463 μm             | /                       | /                       | 25 x 30 μm               |             |

| $(10^{-8} \text{ ohm.cm}^2)$                                  | 7.5            | 72          | 7.51                        | 0.8                     | ~1.6                    | ~2.0                     |             |

Table 2: Benchmark of ohmic contacts on n-InGaAs. Our CMOS-compatible process yields values in line with state-of-the-art for THz HBT [8-9].